![]()

For a current list of our FPGA IP Cores to implement Hardware Acceleration Algorithms, please contact us.

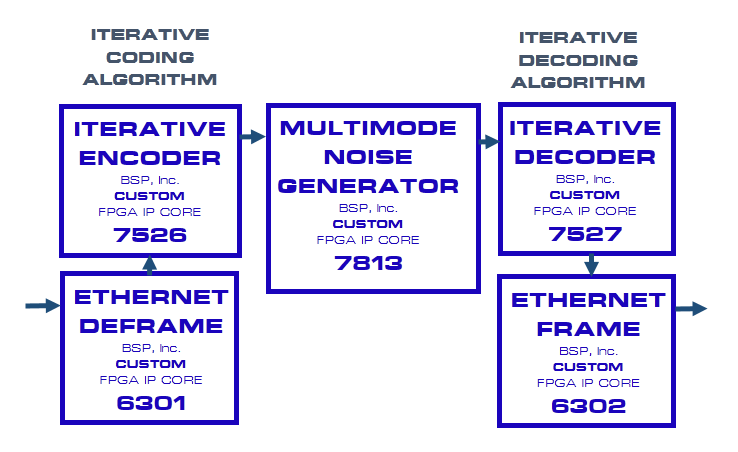

Below is an example combining Blueprint Signal Processing FPGA IP Cores to implement a hardware acceleration algorithm to reduce the research and development time of large error correction codes:

Similar to HPC algorithms, FPGA Hardware Acceleration Algorithms are specific implementations of processing tasks where the use of dedicated FPGA hardware results in a benefit such as off-loading microprocessors and can also be used to add low latency, real-time response in a system. FPGA Hardware Acceleration Algorithms can be combined with COTS FPGA boards to provide a fast, cost effective solution to support design and development efforts. In these situations FPGA Hardware Acceleration Algorithms can save significant Non-Recurring Engineering (NRE) costs.

To learn more about Blueprint Signal Processing FPGA Hardware Acceleration Algorithms please contact us.

MAIN | PURCHASE | LEGAL NOTICES | CONTACT US

© COPYRIGHT 2024, BLUEPRINT SIGNAL PROCESSING, INC.